# UNIT – I

# **Evolution and Architecture of Microprocessors 8085 and 8086**

## 1-1. Evolution of Microprocessor 8085

(i) 4-bit Microprocessors: The first microprocessor was introduced in 1971 by Intel Corp. It was named Intel 4004 as it was a 4 bit processor. It was a processor on a single chip. It could perform simple arithmetic and logic operations such as addition, subtraction, boolean AND and boolean OR. It had a control unit capable of performing control functions like fetching an instruction from memory, decoding it, and generating control pulses to execute it. It was able to operate on 4 bits of data at a time. This first microprocessor was quite a success in industry. Soon other microprocessors were also introduced. Intel introduced the enhanced version of 4004, the 4040. Some other 4 bit processors are International's PPS4 and Thoshiba's T3472.

(ii) 8-bit Microprocessors: The first 8 bit microprocessor which could perform arithmetic and logic operations on 8 bit words was introduced in 1973 again by Intel. This was Intel 8008 and was later followed by an improved version, Intel 8088. Some other 8 bit processors are Zilog-80 and Motorola M6800.

(iii) **16-bit Microprocessors:** The 8-bit processors were followed by 16 bit processors. They are Intel 8086 and 80286.

(iv) **32-bit Microprocessors:** The 32 bit microprocessors were introduced by several companies but the most popular one is Intel 80386.

(v) Pentium Series: Instead of 80586, Intel came out with a new processor namely Pentium processor. Its performance is closer to RISC performance. Pentium was followed by Pentium Pro CPU. Pentium Pro allows allow multiple CPUs in a single system in order to achive multiprocessing. The MMX extension was added to Pentium Pro and the result was Pentiuum II. The low cost version of Pentium II is Celeron. The Pentium III provided high performance floating point operations for certain types of computations by using the SIMD extensions to the instruction set. These new instructions makes the Pentium III faster than high-end RISC CPUs. Interestingly Pentium IV could not execute code faster than the Pentium III when running at the same clock frequency. So Pentium IV had to speed up by executing at a much higher clock frequency.

### **1.2.** Computer & Classification of Computers:

Computer is an electronic device which has many units like Input unit, Control unit and Output unit. Input unit consists of input devices like keyboard, mouse, scanner, light pen, etc., Output unit consists of output devices like printer, monitor, etc., Control unit controls all the actions of computer which consists of memory unit, Arithmetic and logic unit. A computer is one of the most brilliant inventions of mankind. Depending on the processing power and size of computers, they have been classified under various types.

## (a) Classification of Computers on the basis of operational principle

Based on the operational principle of computers, they are categorized as analog, digital and hybrid computers.

(i). Analog Computers: These are almost extinct today. These are different from a digital computer because an analog computer can perform several mathematical operations simultaneously. It uses continuous variables for mathematical operations and utilizes mechanical or electrical energy.

(ii). Digital Computers: They use digital circuits and are designed to operate on two states, namely bits 0 and 1. They are analogous to states ON and OFF. Data on these computers is represented as a series of 0s and 1s. Digital computers are suitable for complex computation and have higher processing speeds. They are programmable. Digital computers are either general purpose computers or special purpose ones. General purpose computers, as their name suggests, are designed for specific types of data processing while general purpose computers are meant for general use.

(iii). Hybrid Computers: These computers are a combination of both digital and analog computers. In this type of computers, the digital segments perform process control by conversion of analog signals to digital ones.

## (b) Classification on the basis of types:

(i). Mainframe Computers: Large organizations use mainframes for highly critical applications such as bulk data processing and ERP. Most of the mainframe computers have capacities to host multiple operating systems and operate as a number of virtual machines. They can substitute for several small servers.

(ii). Microcomputers: A computer with a microprocessor and its central processing unit is known as a microcomputer. They do not occupy space as much as mainframes do. When supplemented with a keyboard and a mouse, microcomputers can be called personal computers. A monitor, a keyboard and other similar input-output devices, computer memory in the form of RAM and a power supply unit come packaged in a microcomputer. These computers can fit on desks or tables and prove to be the best choice for single-user tasks.

(iii). **Personal Computers:** Personal computers come in different forms such as desktops, laptops and personal digital assistants. Let us look at each of these types of computers.

(iv) **Desktops:** A desktop is intended to be used on a single location. The spare parts of a desktop computer are readily available at relatively lower costs. Power consumption is not as critical as that in laptops. Desktops are widely popular for daily use in the workplace and households.

(v)Laptops: Similar in operation to desktops, laptop computers are miniaturized and optimized for mobile use. Laptops run on a single battery or an external adapter that charges the computer batteries. They are enabled with an inbuilt keyboard, touch pad acting as a mouse and a liquid crystal display. Their portability and capacity to operate on battery power have proven to be of great help to mobile users.

(vi) Notebooks: They fall in the category of laptops, but are inexpensive and relatively smaller in size. They had a smaller feature set and lesser capacities in comparison to regular laptops,

(v) Personal Digital Assistants (PDAs): It is a handheld computer and popularly known as a palmtop. It has a touch screen and a memory card for storage of data. PDAs can also be used as portable audio players, web browsers and smart phones. Most of them can access the Internet by means of Bluetooth or Wi-Fi communication.

(vi) Minicomputers: In terms of size and processing capacity, minicomputers lie in between mainframes and microcomputers. Minicomputers are also called mid-range systems or workstations. The term began to be popularly used in the 1960s to refer to relatively smaller third generation computers. They took up the space that would be needed for a refrigerator or two and used transistor and core memory technologies. The 12-bit PDP-8 minicomputer of the Digital Equipment Corporation was the first successful minicomputer.

(vii) Servers: They are computers designed to provide services to client machines in a computer network. They have larger storage capacities and powerful processors. Running on them are programs that serve client requests and allocate resources like memory and time to client machines. Usually they are very large in size, as they have large processors and many hard drives. They are designed to be fail-safe and resistant to crash.

(viii) Supercomputers: The highly calculation-intensive tasks can be effectively performed by means of supercomputers. Quantum physics, mechanics, weather forecasting, molecular theory are best studied by means of supercomputers. Their ability of parallel processing and their well-designed memory hierarchy give the supercomputers, large transaction processing powers.

(ix) Wearable Computers: A record-setting step in the evolution of computers was the creation of wearable computers. These computers can be worn on the body and are often used in the study of behavior modeling and human health. Military and health professionals have incorporated wearable computers into their daily routine, as a part of such studies. When the users' hands and sensory organs are engaged in other activities, wearable computers are of great help in tracking human actions. Wearable computers do not have to be turned on and off and remain in operation without user intervention.

(x) Tablet Computers: Tablets are mobile computers that are very handy to use. They use the

touch screen technology. Tablets come with an onscreen keyboard or use a stylus or a digital pen. Apple's iPad redefined the class of tablet computers.

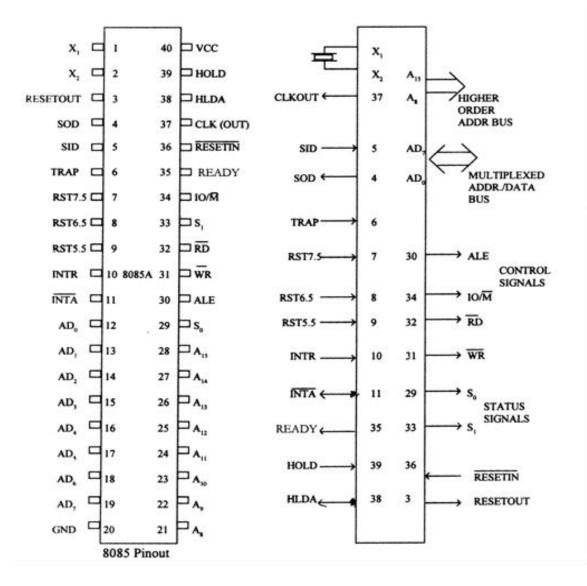

# **1.3.** Pin diagram and Pin description of 8085

8085 is a 40 pin IC, DIP package. The signals from the pins can be grouped as follows

- (i) Power supply and clock signals

- (ii) Address bus

- (iii)Data bus

- (iv)Control and status signals

- (v) Interrupts and externally initiated signals

- (vi) Serial I/O ports

# (i) Power supply and Clock frequency signals:

- Vcc + 5 volt power supply

- Vss Ground

- X1, X2 : Crystal or R/C network or LC network connections to set the frequency of internal clock generator.

- The frequency is internally divided by two. Since the basic operating timing frequency is 3 MHz, a 6 MHz crystal is connected externally.

- CLK (output)-Clock Output is used as the system clock for peripheral and devices interfaced with the microprocessor.

# (ii) Address Bus:

• A8 - A15 (output; 3-state). It carries the most significant 8 bits of the memory address or the 8 bits of the I/O address;

# (iii). Multiplexed Address / Data Bus:

- AD0 AD7 (input/output; 3-state). These multiplexed set of lines used to carry the lower order 8 bit address as well as data bus. During the opcode fetch operation, in the first clock cycle, the lines deliver the lower order address A0 A7.

- In the subsequent IO / memory, read / write clock cycle the lines are used as data bus.

- The CPU may read or write out data through these lines.

# (iv). Control and Status signals:

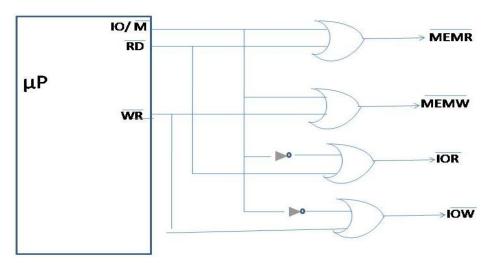

- ALE (output) Address Latch Enable. This signal helps to capture the lower order address presented on the multiplexed address / data bus.

- RD (output 3-state, active low) Read memory or IO device. This indicates that the selected memory location or I/O device is to be read and that the data bus is ready for accepting data from the memory or I/O device.

- WR (output 3-state, active low) Write memory or IO device. This indicates that the data on the data bus is to be written into the selected memory location or I/O device.

- IO/M (output) Select memory or an IO device. This status signal indicates that the read / write operation relates to whether the memory or I/O device. It goes high to indicate an I/O operation.It goes low for memory operations.

### (v). Status Signals:

• It is used to know the type of current operation of the microprocessor.

Fig 1.1(a) - Pin Diagram of 8085 & Fig.1.1(b) - logical schematic of Pin diagram.

| IO/M(Active<br>Low) | S1 | S2 | Data Bus Status (Output) |

|---------------------|----|----|--------------------------|

| 0                   | 0  | 0  | Halt                     |

| 0                   | 0  | 1  | Memory WRITE             |

| 0                   | 1  | 0  | MemoryREAD               |

| 1                   | 0  | 1  | IO WRITE                 |

| 1                   | 1  | 0  | IO READ                  |

| 0                   | 1  | 1  | Opcode fetch             |

| 1                   | 1  | 1  | Interrupt acknowledge    |

#### (vi). Interrupts and Externally initiated operations:

- They are the signals initiated by an external device to request the microprocessor to do a particular task or work.

- There are five hardware interrupts called,

Fig. 1,2

On receipt of an interrupt, the microprocessor acknowledges the interrupt by the active low INTA (Interrupt Acknowledge) signal.

### **READY** (input)

- Memory and I/O devices will have slower response compared to microprocessors.

- Before completing the present job such a slow peripheral may not be able to handle further data or control signal from CPU.

- The processor sets the READY signal after completing the present job to access the data.

- The microprocessor enters into WAIT state while the READY pin is disabled.

### **Direct Memory Access (DMA):**

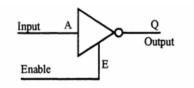

Tri state devices:

Fig. 1.3

• 3 output states are high & low states and additionally a high impedance state. When enable E is high the gate is enabled and the output Q can be 1 or 0 (if A is 0, Q is 1, otherwise Q is 0). However, when E is low the gate is disabled and the output Q entersinto a high impedance state

| Е       | А | Q | State             |

|---------|---|---|-------------------|

| l(high) | 0 | 1 | High              |

| 1       | 1 | 0 | Low               |

| 0(1ow)  | 0 | 0 | High<br>impedance |

| 0       | 1 | 0 | High<br>impedance |

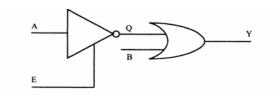

Fig. 1.4

- For both high and low states, the output Q draws a current from the input of the OR gate.

- When E is low, Q enters a high impedance state; high impedance means it is electrically isolated from the OR gate's input, though it is physically connected. Therefore, it does not draw any current from the OR gate's input.

- When 2 or more devices are connected to a common bus, to prevent the devices from interfering with each other, the tristate gates are used to disconnect all devices except the one that is communicating at a given instant.

- The CPU controls the data transfer operation between memory and I/O device. Direct Memory Access operation is used for large volume data transfer between memory and an I/O device directly.

- The CPU is disabled by tri-stating its buses and the transfer is effected directly by external control circuits.

- HOLD signal is generated by the DMA controller circuit. On receipt of this signal, the microprocessor acknowledges the request by sending out HLDA signal and leaves out the control of the buses. After the HLDA signal the DMA controller starts the direct transfer of data.

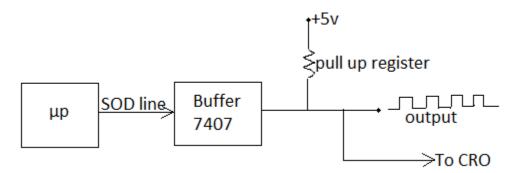

### (vi). Single Bit Serial I/O ports:

- SID (input) Serial input data line

- SOD (output) Serial output data line

- These signals are used for serial communication.

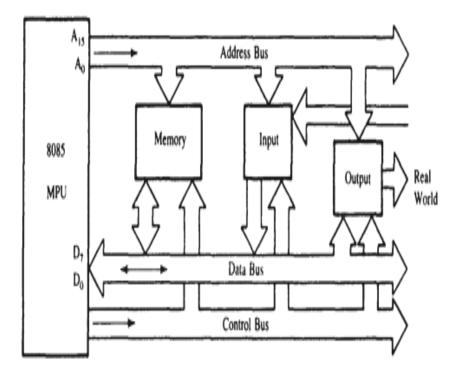

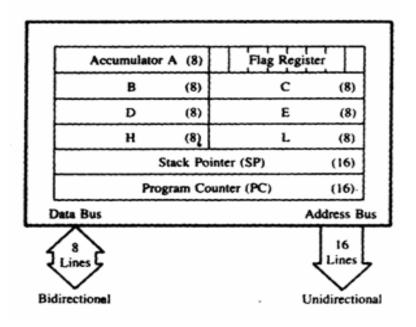

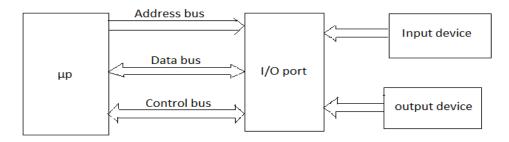

**1.4. Bus Structure of 8085 Microprocessor** : There are three buses in Microprocessor:

1. Address Bus 2. Data Bus . 3. Control Bus

Fig. 1.5: Bus Structure

1.Address Bus:- Genearlly, Microprocessor has 16 bit address bus. The bus over which the CPU sends out the address of the memory location is known as Address bus. The address bus carries the address of memory location to be written or to be read from. The address bus is unidirectional. It means bits flowing occurs only in one direction, only from microprocessor to peripheral devices.

**2. Data Bus**:- 8085 Microprocessor has 8 bit data bus. So it can be used to carry the 8 bit data starting from 0000000H(00H) to 1111111H(FFH). Here 'H' tells the Hexadecimal Number. It is bidirectional. These lines are used for data flowing in both direction means data can be transferred or can be received through these lines. The data bus also connects the I/O ports and CPU. The largest number that can appear on the data bus is 11111111.

**3.Control Bus:-**The control bus is used for sending control signals to the memory and I/O devices. The CPU sends control signal on the control bus to enable the outputs of addressed memory devices or I/O port devices. Some of the control bus signals are as follows:

(i).Memory read (ii) . Memory write (iii). I/O read (iv). I/O write.

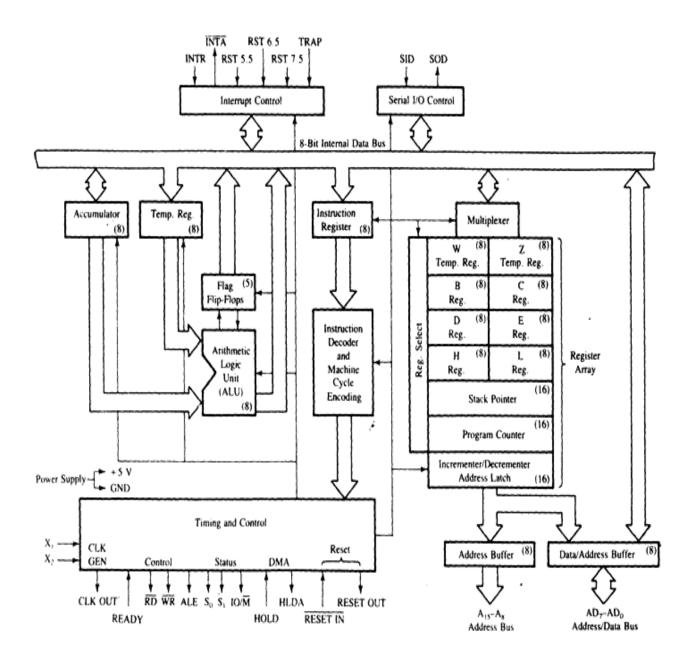

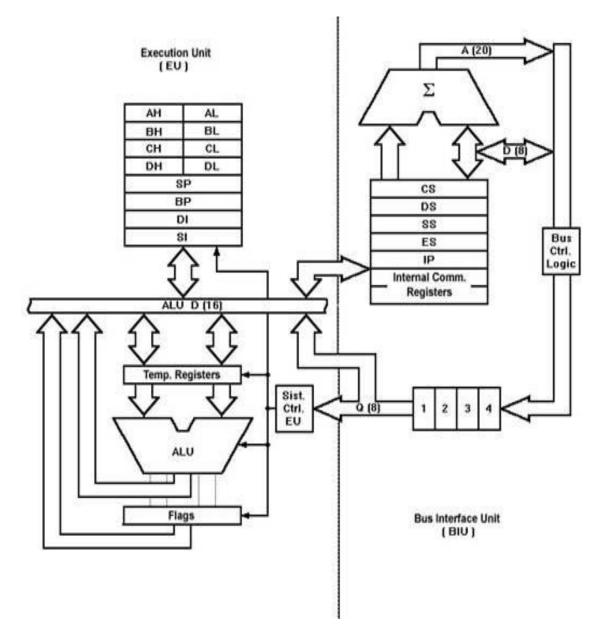

#### 1.5. Architecture of 8085 Microprocessor :

The Functional Block Diagram of 8085 Microprocessor is given below:

Fig. 1.6 Architecture of 8085

Fig.1.7

Acumulator:- It is a 8-bit register which is used to perform airthmetical and logical operation. It stores the output of any operation. It also works as registers for i/o accesses.

**Temporary Register:-** It is a 8-bit register which is used to hold the data on which the acumulator is computing operation. It is also called as operand register because it provides operands to ALU.

**Registers:-** These are general purposes registers. Microprocessor consists 6 general purpose registers of 8-bit each named as B, C, D, E,H and L. Generally theses registers are not used for storing the data permanently. It carries the 8-bits data. These are used only during the execution of the instructions. These registers can also be used to carry the 16 bits data by making the pair of 2 registers. The valid register pairs available are BC, DE HL. We can not use the pairs except BC, DE and HL. These registers are programmed by user.

ALU:-ALU performs the airthmetic operations and logical operation.

**Flag Registers:-**It consists of 5 flip flop which changes its status according to the result stored in an accumulator. It is also known as status registers. It is connected to the ALU. There are five flip-flops in the flag register are as follows:

1.Sign(S) 2.Zero (Z) 3.Auxiliary carry (AC) 4.Parity (P) 5.Carry (C)

The bit position of the flip flop in flag register is:

| D <sub>7</sub> | $D_6$ | Ds | D4 | D3 | $D_2$ | $D_1$ | $D_0$ |

|----------------|-------|----|----|----|-------|-------|-------|

| S              | Ζ     |    | AC |    | Р     |       | СҮ    |

All of the three flip flop set and reset according to the stored result in the accumulator.

*1. Sign-* If D7 of the result is 1 then sign flag is set otherwise reset. As we know that a number on the D7 always desides the sign of the number.

if D7 is 1: the number is negative.

if D7 is 0: the number is positive.

2. *Zeros* (*Z*)-If the result stored in an accumulator is zero then this flip flop is set otherwise it is reset.

*3.Auxiliary carry(AC)*-If any carry goes from D3 to D4 in the output then it is set otherwise it is reset.

4.*Parity*(*P*)-If the no of 1's is even in the output stored in the accumulator then it is set otherwise it is reset for the odd.

5. Carry(C)-If the result stored in an accumulator generates a carry in its final output then it is set otherwise it is reset.

**Instruction registers(IR):-**It is a 8-bit register. When an instruction is fetched from memory then it is stored in this register.

**Instruction Decoder:-** Instruction decoder identifies the instructions. It takes the informations from instruction register and decodes the instruction to be performed.

**Program Counter:**-It is a 16 bit register used as memory pointer. It stores the memory address of the next instruction to be executed. So we can say that this register is used to sequencing the program. Generally the memory have 16 bit addresses so that it has 16 bit memory. The program counter is set to 0000H.

**Stack Pointer:**-It is also a 16 bit register used as memory pointer. It points to the memory location called stack. Generally stack is a reserved portion of memory where information can be stores or taken back together.

**Timing and Control Unit**:-It provides timing and control signal to the microprocessor to perform the various operation. It has three control signal. It controls all external and internal circuits. It operates with reference to clock signal. It synchronizes all the data transfers.

There are three control signal:

*1.ALE*-Airthmetic Latch Enable, It provides control signal to synchronize the components of microprocessor.

2.RD- This is active low used for reading operation.

*3.WR*-This is active low used for writing operation. There are three status signal used in microprocessor S0, S1 and IO/M. It changes its status according the provided input to these pins.

| IO/M(Active<br>Low) | S1 | S2 | Data Bus Status(Output) |

|---------------------|----|----|-------------------------|

| 0                   | 0  | 0  | Halt                    |

| 0                   | 0  | 1  | Memory WRITE            |

| 0                   | 1  | 0  | Memory READ             |

| 1                   | 0  | 1  | IO WRITE                |

| 1                   | 1  | 0  | IO READ                 |

| 0                   | 1  | 1  | Opcode fetch            |

| 1                   | 1  | 1  | Interrupt acknowledge   |

**Serial Input Output Control**-There are two pins in this unit. This unit is used for serial data communication.

**Interrupt Unit**-There are 6 interrupt pins in this unit. Generally an external hardware is connected to these pins. These pins provide interrupt signal sent by external hardware to microprocessor and microprocessor sends acknowledgement for receiving the interrupt signal. Generally INTA is used for acknowledgement.

### 8085- Registers

The 8085 has six general purpose registers to store 8 bit data. These are identified as B, C, D, E, H, L. they can be combined as register pairs BC, DE, and HL, to perform 16 bit operations.

## Accumulator

The acc is an 8 bit register that is part of the arithmetic logic unit [ALU]. This register is used to store 8 bit data and to perform arithmetic and logical operations. The result of the operation is stored in the accumulator and identified as A.

## Flags

The arithmetic logic unit [ALU] includes 5 flip flops which are set or reset after an operation according to data conditions of the result in the accumulator and other registers. They are called zero (Z), carry (CY), sign(S), parity (P), and auxiliary carry (AC). The microprocessor used these flags to test data conditions.

## **Program counter**

The microprocessor uses the PC register to sequence the execution of the instructions. The function of the PC is to point to the memory address from which the next byte is to be fetched. When a byte is being fetched, the pc is increased by one to point to the next memory location.

## **Stack pointer**

The SP is also a 16 bit register used as a memory pointer. It points to a memory location in R/W memory, called the *stack*

## **Interrupts In 8085**

## What is Interrupt?

Interrupt is a mechanism by which an I/O or an instruction can suspend the normal execution of processor and get itself serviced. Generally, a particular task is assigned to that interrupt signal. In the microprocessor based system the interrupts are used for data transfer between the peripheral devices and the microprocessor.

## Interrupt Service Routine(ISR)

Interrupt means to break the sequence of operation. While the CPU is executing a program an interrupt breaks the normal sequence of execution of instructions & diverts its execution to some other program. This program to which the control is transferred is called the *interrupt service routine*. A small program or a routine that when executed services the corresponding interrupting source is called as an ISR.

### **Execution of Interrupts**

When there is an interrupt requests to the Microprocessor then after accepting the interrupts Microprocessor send the INTA (active low) signal to the peripheral. The vectored address of particular interrupt is stored in program counter. The processor executes an interrupt service routine (ISR) addressed in program counter.

There are two types of interrupts used in 8085 Microprocessor:

Hardware Interrupts and Software Interrupts

## **Software Interrupts**

A software interrupts is a particular instructions that can be inserted into the desired location in the rpogram. There are eight Software interrupts in 8085 Microprocessor. From RST0 to RST7.

RST0, RST1, RST2, RST3, RST4, RST5, RST6, RST7

They allow the microprocessor to transfer program control from the main program to the subroutine program. After completing the subroutine program, the program control returns back to the main program.

## **Hardware Interrupts**

There are 6 interrupt pins in the microprocessor used as Hardware Interrupts given below:

TRAP, RST7.5, RST6.5, RST5.5, INTR

Note:

INTA is not an interrupt. INTA is used by the Microprocessor for sending the acknowledgement. TRAP has highest priority and RST7.5 has second highest priority and so on.

## TRAP

It is non maskable edge and level triggered interrupt. TRAP has the highest priority and vectored interrupt. Edge and level triggered means that the TRAP must go high and remain high until it is acknowledged. In case of sudden power failure, it executes a ISR and send the data from main memory to backup memory.

As we know that TRAP can not be masked but it can be delayed using HOLD signal. This interrupt transfers the microprocessor's control to location 0024H.

TRAP interrupts can only be masked by reseting the microprocessor. There is no other way to mask it.

## *RST7.5*

It has the second highest priority. It is maskable and edge level triggered interrupt. The vector address of this interrupt is 003CH. Edge sensitive means input goes high and no need to maintain high state until it is recognized. It can also be reset or masked by reseting microprocessor. It can also be resetted by DI instruction.

## RST6.5 and RST5.5

These are level triggered and maskable interrupts. When RST6.5 pin is at logic 1, INTE flip-flop is set. RST 6.5 has third highest priority and RST 5.5 has fourth highest priority.

It can be masked by giving DI and SIM instructions or by reseting microprocessor.

INTR

It is level triggered and maskable interrupt. The following sequence of events occurs when INTR signal goes high. The 8085 checks the status of INTR signal during execution of each instruction. If INTR signal is high, then 8085 complete its current instruction and sends active low interrupt acknowledge signal, if the interrupt is enabled. On receiving the instruction, the 8085 save the address of next instruction on stack and execute received instruction. It has the lowest priority. It can be disabled by reseting the microprocessor or by DI and SIM instruction.

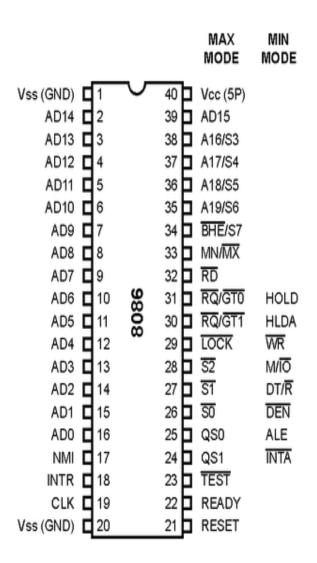

## 1.6. Intel 8086 Microprocessor:

### **Pin Diagram:**

Fig. 1.8 Pin diagram of 8086 micprocessor

The 8086 can operate in two modes these are the minimum mode and maximum mode. For minimum mode, a unique processor system with a single 8086 and for Maximum mode a multi processor system with more than one 8086. The following pin function descriptions are for the microprocessor 8086 in either minimum or maximum mode.

#### AD0 - AD15 (I/O): Address Data Bus

These lines constitute the time multiplexed memory/IO address during the first clock cycle (T1) and data during T2, T3 and T4 clock cycles. A0 is analogous to BHE for the lower byte of the data bus, pins D0-D7. A0 bit is Low during T1 state when a byte is to be transferred on the lower portion of the bus in memory or I/O operations. 8-bit oriented devices tied to the lower half would normally use A0 to condition chip select functions. These lines are active high and float to tri-state during interrupt acknowledge and local bus "Hold acknowledge".

### A19/S6, A18/S5, A17/S4, A16/S3 (0): Address/Status

During T1 state these lines are the four most significant address lines for memory operations. During I/O operations these lines are low. During memory and I/O operations, status information is available on these lines during T2, T3, and T4 states.S5: The status of the interrupt enable flag bit is updated at the beginning of each cycle. The status of the flag is indicated through this bus.

**S6:** When Low, it indicates that 8086 is in control of the bus. During a "Hold acknowledge" clock period, the 8086 tri-states the S6 pin and thus allows another bus master to take control of the status bus.

### S3 & S4:

Lines are decoded as follows:

| A17/S4 | A16/S3 | Function             |

|--------|--------|----------------------|

| 0      | 0      | Extra segment access |

| 0      | 1      | Stack segment access |

| 1      | 0      | Code segment access  |

| 1      | 1      | Data segment access  |

|        |        |                      |

After the first clock cycle of an instruction execution, the A17/S4 and A16/S3 pins specify which segment register generates the segment portion of the 8086 address. Thus by decoding these lines and using the decoder outputs as chip selects for memory chips, up to 4 Megabytes (one Mega per segment) of memory can be accesses. This feature also provides a degree of protection by

preventing write operations to one segment from erroneously overlapping into another segment and destroying information in that segment.

**BHE /S7 (O): Bus High Enable/Status:** During T1 state the BHE should be used to enable data onto the most significant half of the data bus, pins D15 - D8. Eight-bit oriented devices tied to the upper half of the bus would normally use BHE to control chip select functions. BHE is Low during T1 state of read, write and interrupt acknowledge cycles when a byte is to be transferred on the high portion of the bus.

The S7 status information is available during T2, T3 and T4 states. The signal is active Low and floats to 3-state during "hold" state. This pin is Low during T1 state for the first interrupt acknowledge cycle.

**RD** (O): **READ**: The Read strobe indicates that the processor is performing a memory or I/O read cycle. This signal is active low during T2 and T3 states and the Tw states of any read cycle. This signal floats to tri-state in "hold acknowledge cycle".

**TEST (I):** TEST pin is examined by the "WAIT" instruction. If the TEST pin is Low, execution continues. Otherwise the processor waits in an "idle" state. This input is synchronized internally during each clock cycle on the leading edge of CLK.

**INTR (I):** Interrupt Request: It is a level triggered input which is sampled during the last clock cycle of each instruction to determine if the processor should enter into an interrupt acknowledge operation. A subroutine is vectored to via an interrupt vector look up table located in system memory. It can be internally masked by software resetting the interrupt enable bit INTR is internally synchronized. This signal is active HIGH.

**NMI (I):** Non-Maskable Interrupt: An edge triggered input, causes a type-2 interrupt. A subroutine is vectored to via the interrupt vector look up table located in system memory. NMI is not maskable internally by software. A transition from a LOW to HIGH on this pin initiates the interrupt at the end of the current instruction. This input is internally synchronized.

**Reset (I):** Reset causes the processor to immediately terminate its present activity. To be recognised, the signal must be active high for at least four clock cycles, except after power-on which requires a 50 Micro Sec. pulse. It causes the 8086 to initialize registers DS, SS, ES, IP and flags to all zeros. It also initializes CS to FFFF H. Upon removal of the RESET signal from the RESET pin, the 8086 will fetch its next instruction from the 20 bit physical address FFFF0H. The reset signal to 8086 can be generated by the 8284. (Clock generation chip). To guarantee reset from power-up, the reset input must remain below 1.5 volts for 50 Micro sec. after Vcc has reached the minimum supply voltage of 4.5V.

**Ready** (I): Ready is the acknowledgement from the addressed memory or I/O device that it will complete the data transfer. The READY signal from memory or I/O is synchronized by the 8284 clock generator to form READY. This signal is active HIGH. The 8086 READY input is not synchronized. Correct operation is not guaranteed if the setup and hold times are not met.

**CLK (I): Clock:** Clock provides the basic timing for the processor and bus controller. It is asymmetric with 33% duty cycle to provide optimized internal timing. Minimum frequency of 2 MHz is required, since the design of 8086 processors incorporates dynamic cells. The maximum clock frequencies of the 8086-4, 8086 and 8086-2 are4MHz, 5MHz and 8MHz respectively. Since the 8086 does not have on-chip clock generation circuitry, and 8284 clock generator chip must be connected to the 8086 clock pin. The crystal connected to 8284 must have a frequency 3 times the 8086 internal frequency. The 8284 clock generation chip is used to generate READY, RESET and CLK.

# MN/MX (I): Maximum / Minimum:

This pin indicates what mode the processor is to operate in. In minimum mode, the 8086 itself generates all bus control signals. In maximum mode the three status signals are to be decoded to generate all the bus control signals.

**Minimum Mode Pins :** The following 8 pins function descriptions are for the 8086 in minimum mode; MN/MX = 1. The corresponding 8 pins function descriptions for maximum mode is explained later.

(i) M/IO (O): Status line: This pin is used to distinguish a memory access or an I/O accesses. When this pin is Low, it accesses I/O and when high it access memory. M / IO becomes valid in the T4 state preceding a bus cycle and remains valid until the final T4 of the cycle. M/IO floats to 3 - state OFF during local bus "hold acknowledge".

(ii) WR (O): Write: Indicates that the processor is performing a write memory or write IO cycle, depending on the state of the M /IOsignal. WR is active for T2, T3 and Tw of any write cycle. It is active LOW, and floats to 3-state OFF during local bus "hold acknowledge ".

(iii) INTA (O): Interrupt Acknowledge: It is used as a read strobe for interrupt acknowledge cycles. It is active LOW during T2, T3, and T4 of each interrupt acknowledge cycle.

(iv) ALE (O): Address Latch Enable: ALE is provided by the processor to latch the address into the 8282/8283 address latch. It is an active high pulse during T1 of any bus cycle. ALE signal is never floated.

(v) DT/ R (O): DATA Transmit/Receive: In minimum mode, 8286/8287 transceiver is used for the data bus. DT/ R is used to control the direction of data flow through the transceiver. This signal floats to tri-state off during local bus "hold acknowledge".

(vi) DEN (O): Data Enable: It is provided as an output enable for the 8286/8287 in a minimum system which uses the transceiver. DEN is active LOW during each memory and IO access. It will be low beginning with T2 until the middle of T4, while for a write cycle, it is active from the beginning of T2 until the middle of T4. It floats to tri-state off during local bus "hold acknowledge".

(vii) HOLD & HLDA (I/O): Hold and Hold Acknowledge: Hold indicates that another master is requesting a local bus "HOLD". To be acknowledged, HOLD must be active HIGH. The processor receiving the "HOLD " request will issue HLDA (HIGH) as an acknowledgement in the middle of the T1-clock cycle. Simultaneous with the issue of HLDA, the processor will float the local bus and control lines. After "HOLD" is detected as being Low, the processor will lower the HLDA and when the processor needs to run another cycle, it will again drive the local bus and control lines.

**Maximum Mode** : The following pins function descriptions are for the 8086/8088 systems in maximum mode (i.e., MN/MX = 0). Only the pins which are unique to maximum mode are described below.

(i) S2, S1, S0 (O): Status Pins: These pins are active during T4, T1 and T2 states and is returned to passive state (1,1,1 during T3 or Tw (when ready is inactive). These are used by the 8288 bus controller to generate all memory and I/O operation) access control signals. Any change by S2, S1, S0 during T4 is used to indicate the beginning of a bus cycle. These status lines are encoded as shown in table 1.1.

### Table 1.1:

| <b>S2</b> | <b>S1</b> | <b>S0</b> | Chracteristics                |

|-----------|-----------|-----------|-------------------------------|

| 0         | 0         | 0         | Interrupt acknowledge         |

| 0         | 0         | 1         | Read I/O port                 |

| 0         | 1         | 0         | Write I/O port                |

| 0         | 1         | 1         | Halt                          |

| 1         | 0         | 0         | Code access 1 0 1 Read memory |

| 1         | 1         | 0         | Write memory                  |

| 1         | 1         | 1         | Passive state                 |

(ii) QS0, QS1 (O): Queue – Status: Queue Status is valid during the clock cycle after which the queue operation is performed. QS0, QS1 provide status to allow external tracking of the internal 8086 instruction queue. The condition of queue status is shown in table 1.2. Queue status

allows external devices like In-circuit Emulators or special instruction set extension coprocessors to track the CPU instruction execution. Since instructions are executed from the 8086 internal queue, the queue status is presented each CPU clock cycle and is not related to the bus cycle activity. This mechanism allows (1) A processor to detect execution of a ESCAPE instruction which directs the co- processor to perform a specific task and (2) An in-circuit Emulator to trap execution of a specific memory location.

## Table:1.2

| QS0 | QS1 | Chracteristics                  |

|-----|-----|---------------------------------|

| 0   | 0   | No operation                    |

| 0   | 1   | First byte of opcode from queue |

| 1   | 0   | Empty the queue                 |

| 1   | 1   | Subsequent byte from queue      |

|     |     |                                 |

(iii) LOCK (O): It indicates to another system bus master, not to gain control of the system bus while LOCK is active Low. The LOCK signal is activated by the "LOCK" prefix instruction and remains active until the completion of the instruction. This signal is active Low and floats to tristate OFF during 'hold acknowledge'.

Example: LOCK XCHG reg., Memory ; Register is any register and memory GT0 ; is the address of the semaphore.

(iv) **RQ/GT0 and RQ/GT1 (I/O): Request/Grant:** These pins are used by other processors in a multi processor organization. Local bus masters of other processors force the processor to release the local bus at the end of the processors current bus cycle. Each pin is bi-directional and has an internal pull up resistors. Hence they may be left un-connected.

## 1.7. General purpose registers

8086 CPU has 8 general purpose registers, each register has its own name:

- **AX** the accumulator register (divided into **AH** / **AL**):

- Generates shortest machine code

- Arithmetic, logic and data transfer

- One number must be in AL or AX

- Multiplication & Division

- Input & Output

- **BX** the base address register (divided into **BH** / **BL**).

- **CX** the count register (divided into **CH** / **CL**):

- Iterative code segments using the LOOP instruction

- Repetitive operations on strings with the REP command

- Count (in CL) of bits to shift and rotate

- **DX** the data register (divided into **DH** / **DL**):

DX:AX concatenated into 32-bit register for some MUL and DIV operations Specifying ports in some IN and OUT operations

- **SI** source index register:

- Can be used for pointer addressing of data

- Used as source in some string processing instructions

- Offset address relative to DS

• **DI** - destination index register: Can be used for pointer addressing of data used as destination in some string processing instructions.

Offset address relative to ES

- **BP** base pointer:

- Primarily used to access parameters passed via the stack

- Offset address relative to SS

- **SP** stack pointer:

- Always points to top item on the stack

- Offset address relative to SS

- Always points to word (byte at even address)

- An empty stack will had SP = FFFEh

### **1.8. Segment registers**

- CS points at the segment containing the current program.

- **DS** generally points at segment where variables are defined.

- **ES** extra segment register, it's up to a coder to define its usage.

- **SS** points at the segment containing the stack.

Although it is possible to store any data in the segment registers, this is never a good idea. The segment registers have a very special purpose - pointing at accessible blocks of memory.

Segment registers work together with general purpose register to access any memory value. For example if we would like to access memory at the physical address **12345h** (hexadecimal), we should set the **DS** = **1230h** and **SI** = **0045h**. This is good, since this way we can access much more memory than with a single register that is limited to 16 bit values. CPU makes a calculation of physical address by multiplying the segment register by 10h and adding general purpose register to it (1230h \* 10h + 45h = 12345h): The address formed with 2 registers is called an **effective address**. By default **BX**, **SI** and **DI** registers work with **DS** segment register; **BP** and **SP** work with **SS** segment register. Other general purpose registers cannot form an effective address. Also, although **BX** can form an effective address, **BH** and **BL** cannot.

## **1.9.** Special purpose registers

- **IP** the instruction pointer:

- Always points to next instruction to be executed

- Offset address relative to CS

**IP** register always works together with **CS** segment register and it points to currently executing instruction.

## 1.10. Register

• Flags Register - determines the current state of the processor.

Flags Register is modified automatically by CPU after mathematical operations, this allows to determine the type of the result, and to determine conditions to transfer control to other parts of the program. Generally we cannot access these registers directly.

- **Carry Flag (CF)** this flag is set to **1** when there is an unsigned overflow. For example when you add bytes 255 + 1 (result is not in range 0...255). When there is no overflow this flag is set to 0.

- **Parity Flag (PF)** this flag is set to 1 when there is even number of one bits in result, and to 0 when there is odd number of one bits. Even if result is a word only 8 low bits are analyzed.

- Auxiliary Flag (AF) set to 1 when there is an unsigned overflow for low nibble (4 bits).

- Zero Flag (ZF) set to 1 when result is zero. For none zero result this flag is set to 0.

- Sign Flag (SF) set to 1 when result is negative. When result is positive it is set to 0. Actually this flag take the value of the most significant bit.

- **Trap Flag (TF)** Used for on-chip debugging.

- Interrupt enable Flag (IF) when this flag is set to 1 CPU reacts to interrupts from external devices.

- **Direction Flag (DF)** this flag is used by some instructions to process data chains, when this flag is set to 0 the processing is done forward, when this flag is set to 1 the processing is done backward.

- **Overflow Flag (OF)** set to 1 when there is a signed overflow. For example, when you add bytes 100 + 50 (result is not in range -128...127).

- Flags Instructions

- CLI Clear Interrupt Flag

- CLD Clear Direction Flag

- CLC Clear Carry Flag

- STC Set Interrupt Flag

- STD Set Direction Flag

- STC Set Carry Flag

### 1.11. Interrupts of 8086

There are two main types of interrupt in the 8086 microprocessor, internal and external hardware interrupts. Hardware interrupts occur when a peripheral device asserts an interrupt input pin of the microprocessor. Whereas internal interrupts are initiated by the state of the CPU (e.g. divide by zero error) or by an instruction.

Provided the interrupt is permitted, it will be acknowledged by the processor at the end of the current memory cycle. The processor then services the interrupt by branching to a special service routine written to handle that particular interrupt. Upon servicing the device, the processor is then instructed to continue with what is was doing previously by use of the "return from interrupt" instruction.

The status of the programme being executed must first be saved. The processors registers will be saved on the stack, or, at very least, the programme counter will be saved. Preserving those registers which are not saved will be the responsibility of the interrupt service routine. Once the programme counter has been saved, the processor will branch to the address of the service routine.

## (i) Edge or Level sensitive Interrupts

Edge level interrupts are recognised on the falling or rising edge of the input signal. They are generally used for high priority interrupts and are latched internally inside the processor. If this latching was not done, the processor could easily miss the falling edge (due to its short duration) and thus not respond to the interrupt request.

Level sensitive interrupts overcome the problem of latching, in that the requesting device holds the interrupt line at a specified logic state (normally logic zero) till the processor acknowledges the interrupt. This type of interrupt can be shared by other devices in a wired 'OR' configuration, which is commonly used to support daisy chaining and other techniques.

### (ii) Maskable Interrupts

The processor can inhibit certain types of interrupts by use of a special interrupt mask bit. This mask bit is part of the flags/condition code register, or a special interrupt register. In the 8086

microprocessor if this bit is clear, and an interrupt request occurs on the Interrupt Request input, it is ignored.

## (iii) Non-Maskable Interrupts

There are some interrupts which cannot be masked out or ignored by the processor. These are associated with high priority tasks which cannot be ignored (like memory parity or bus faults). In general, most processors support the Non-Maskable Interrupt (NMI). This interrupt has absolute priority, and when it occurs, the processor will finish the current memory cycle, then branch to a special routine written to handle the interrupt request.

## (iv) Advantages of Interrupts

Interrupts are used to ensure adequate service response times by the processing. Sometimes, with software polling routines, service times by the processor cannot be guaranteed, and data may be lost. The use of interrupts guarantees that the processor will service the request within a specified time period, reducing the likelihood of lost data.

## (v) Interrupt Latency

The time interval from when the interrupt is first asserted to the time the CPU recognises it. This will depend much upon whether interrupts are disabled, prioritized and what the processor is currently executing. At times, a processor might ignore requests whilst executing some indivisible instruction stream (read-write-modify cycle). The figure that matters most is the longest possible interrupt latency time.

### (vi) Interrupt Response Time

The time interval between the CPU recognising the interrupt to the time when the first instruction of the interrupt service routine is executed. This is determined by the processor architecture and clock speed.

# **UNIT-II**

# Instruction set of 8085 and Assembly language Programming

## 2.1. Software:

Software is a collection of instructions that enable the user to interact with a computer, its hardware, or perform tasks. Without software, computers would be useless.

Examples and types of software: Below is a list of the different kinds of software

| <u>Software</u>           | <u>Example</u>                            |

|---------------------------|-------------------------------------------|

| 1. Antivirus              | AVG, McAfee, Housecall                    |

| 2. Email                  | Outlook, Thunderbird                      |

| 3. Operating systems      | Mac OS X10, Windows XP, Windows 7         |

| 4.Database                | Accsee, MySQL, SQL                        |

| 5. Audio/music program    | iTunes, WinAmp                            |

| 6. Spreadsheet            | Excel                                     |

| 7. Wordprocessor          | Word                                      |

| 8. Programming languages  | C++, Java, HTML, VB, Fortran, Perl        |

| 9. Internet browser       | Firefox, Google Chrome, Internet Explorer |

| 10. Photo/Graphis program | Adobe Photoshop, CorelDraw                |

## 2.2. What is Assembly Language?

Assembly language is a low-level programming language for a computer. Assembly language is converted into executable machine code by a utility program referred to as an assembler like NASM, MASM, etc.

## 2.3 Advantages of Assembly Language

Having an understanding of assembly language makes one aware of -

- How programs interface with OS, processor, and BIOS;

- How data is represented in memory and other external devices;

- How the processor accesses and executes instruction;

- How instructions access and process data;

- How a program accesses external devices.

## Other advantages of using assembly language are -

- It requires less memory and execution time;

- It allows hardware-specific complex jobs in an easier way;

- It is suitable for time-critical jobs;

• It is most suitable for writing interrupt service routines and other memory resident program.

## 2.3. Assembler:

An assembler program creates object code by translating combinations of mnemonics and syntax for operations and addressing modes into their numerical equivalents. This representation typically includes an *operation code* ("opcode") as well as other control bits and data. The assembler also calculates constant expressions and resolves symbolic names for memory locations and other entities. Most assemblers also include macro facilities for performing textual substitution – e.g., to generate common short sequences of instructions as inline, instead of *called* subroutines.

Some assemblers may also be able to perform some simple types of instruction set-specific optimizations. One concrete example of this may be the ubiquitous x86 assemblers from various vendors. Most of them are able to perform jump-instruction replacements (long jumps replaced by short or relative jumps) in any number of passes, on request.

Like early programming languages such as Fortran, Algol, Cobol and Lisp, assemblers have been available since the 1950s and the first generations of text based computer interfaces. There may be several assemblers with different syntax for a particular CPU or instruction set architecture. For instance, an instruction to add memory data to a register in a x86-family processor might be add eax, [ebx], in original *Intel syntax*, whereas this would be written addl (%ebx), %eax in the AT&T syntax used by the GNU Assembler.

## Number of passes

There are two types of assemblers based on how many passes through the source are needed to produce the executable program.

- One-pass assemblers go through the source code once. Any symbol used before it is defined will require "errata" at the end of the object code (or, at least, no earlier than the point where the symbol is defined) telling the linker or the loader to "go back" and overwrite a placeholder which had been left where the as yet undefined symbol was used.

- Multi-pass assemblers create a table with all symbols and their values in the first passes, then use the table in later passes to generate code.

In both cases, the assembler must be able to determine the size of each instruction on the initial passes in order to calculate the addresses of subsequent symbols. The original reason for the use of one-pass assemblers was speed of assembly – often a second pass would require rewinding and rereading the program source on tape or rereading a deck of cards or punched paper tape. With modern computers this has ceased to be an issue. The advantage of the multi-pass assembler is that the absence of errata makes the linking process faster.

**High-level assemplers:** More sophisticated high-level assemblers provide language abstractions such as:

- High-level procedure/function declarations and invocations

- Advanced control structures

- High-level abstract data types, including structures/records, unions, classes, and sets

- Sophisticated macro processing

- Object-oriented programming features such as classes, objects, abstraction, polymorphism, and inheritance.

### 2.4. Assembler directives:

Assembly directives, also called pseudo-opcodes, pseudo-operations or pseudo-ops, are commands given to an assembler "directing it to perform operations other than assembling instructions." Directives affect how the assembler operates and "may affect the object code, the symbol table, the listing file, and the values of internal assembler parameters." Sometimes the term pseudo-opcode is reserved for directives that generate object code, such as those that generate data. The names of pseudo-ops often start with a dot to distinguish them from machine instructions. Pseudo-ops can make the assembly of the program dependent on parameters input by a programmer, so that one program can be assembled different ways, perhaps for different applications. Or, a pseudo-op can be used to manipulate presentation of a program to make it easier to read and maintain. Another common use of pseudo-ops is to reserve storage areas for run-time data and optionally initialize their contents to known values.

Symbolic assemblers let programmers associate arbitrary names (*labels* or *symbols*) with memory locations and various constants. Usually, every constant and variable is given a name so instructions can reference those locations by name, thus promoting self-documenting code. In executable code, the name of each subroutine is associated with its entry point, so any calls to a subroutine can use its name. Inside subroutines, GOTO destinations are given labels. Some assemblers support *local symbols* which are lexically distinct from normal symbols (e.g., the use of "10\$" as a GOTO destination).

Some assemblers, such as NASM provide flexible symbol management, letting programmers manage different namespaces, automatically calculate offsets within data structures, and assign labels that refer to literal values or the result of simple computations performed by the assembler. Labels can also be used to initialize constants and variables with relocatable addresses.

Assembly languages, like most other computer languages, allow comments to be added to program source code that will be ignored during assembly. Judicious commenting is essential in assembly language programs, as the meaning and purpose of a sequence of binary machine instructions can be difficult to determine. The "raw" (uncommented) assembly language generated by compilers or disassemblers is quite difficult to read when changes must be made.

### 2.5. The 8085 Addressing Modes :

The instructions MOV B, A or MVI A, 82H are to copy data from a source into a destination. In these instructions the source can be a register, an input port, or an 8-bit number (00H to FFH). Similarly, a destination can be a register or an output port. The sources and destination are

operands. The various formats for specifying operands are called the *addressing modes*. For 8085, they are:

- (i). Immediate addressing.

- (ii) Register addressing.

- (iii) Direct addressing.

- (iv) Indirect addressing.

### (i) Immediate addressing:

Data is present in the instruction. Load the immediate data to the destination provided.

Example: MVI R, data

### (ii) Register addressing :

Data is provided through the registers. Example: MOV Rd, Rs

### (iii) Direct addressing:

Used to accept data from outside devices to store in the accumulator or send the data stored in the accumulator to the outside device. Accept the data from the port 00H and store them into the accumulator or send the data from the accumulator to the port 01H.

Example: IN 00H or OUT 01H

### (iv) Indirect Addressing:

This means that the Effective Address is calculated by the processor. And the contents of the address is used to form a second address. The second address is where the data is stored. Note that this equires several memory accesses; two accesses to retrieve the 16-bit address and a further access (or accesses) to retrieve the data which is to be loaded into the register.

### 2.6. Instruction Set Classification:

An instruction is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions, called the instruction set, determines what functions the microprocessor can perform. These instructions can be classified into the following five functional categories: data transfer (copy) operations, arithmetic operations, logical operations, branching operations, and machine-control operations.

## (i) Data Transfer (Copy) Operations:

This group of instructions copy data from a location called a source to another location called a destination, without modifying the contents of the source. The various types of data transfer (copy) are listed below together with examples of each type:

#### Types

#### Examples

| 1. Between Registers.                         | 1. Copy the contents of the register B into register D.     |

|-----------------------------------------------|-------------------------------------------------------------|

| 2. Specific data byte 32H to a register       | 2. Load register B with the data byte or a memory location. |

| 3. Between a memory location and a register.  | 3. From a memory location 2000H to register B.              |

| 4. Between an I/O device and the accumulator. | 4. From an input keyboard to the accumulator.               |

(*ii*) *Arithmetic Operations* These instructions perform arithmetic operations such as addition, subtraction, increment, and decrement.

*Addition* - Any 8-bit number, or the contents of a register or the contents of a memory location can be added to the contents of the accumulator and the sum is stored in the accumulator. No two other 8-bit registers can be added directly (e.g., the contents of register B cannot be added directly to the contents of the register C). The instruction DAD is an exception; it adds 16-bit data directly in register pairs.

*Subtraction* – Any 8-bit number, or the contents of a register, or the contents of a memory location can be subtracted from the contents of the accumulator and the results stored in the accumulator. The subtraction is performed in 2's complement, and the results if negative, are expressed in 2's complement. No two other registers can be subtracted directly.

**Increment/Decrement** - The 8-bit contents of a register or a memory location can be incremented or decrement by 1. Similarly, the 16-bit contents of a register pair (such as BC) can be incremented or decrement by 1. These increment and decrement operations differ from addition and subtraction in an important way; i.e., they can be performed in any one of the registers or in a memory location.

(*iii*) *Logical Operations* : These instructions perform various logical operations with the contents of the accumulator. AND, OR, Exclusive-OR. Any 8-bit number, or the contents of a register, or of a memory location can be logically ANDed, Ored, or Exclusive-ORed with the contents of the accumulator. The results are stored in the ccumulator.

*Rotate*- Each bit in the accumulator can be shifted either left or right to the next position.

*Compare-* Any 8-bit number, or the contents of a register, or a memory location can be compared for equality, greater than, or less than, with the contents of the accumulator.

*Complement* - The contents of the accumulator can be complemented. All 0s are replaced by 1s and all 1s are replaced by 0s.

*(iv) Branching Operations :* This group of instructions alters the sequence of program execution either conditionally or unconditionally.

*Jump* - Conditional jumps are an important aspect of the decision-making process in the programming. These instructions test for a certain conditions (e.g., Zero or Carry flag) and alter the program sequence when the condition is met. In addition, the instruction set includes an instruction called unconditional jump.

*Call, Return, and Restart* - These instructions change the sequence of a program either by calling a subroutine or returning from a subroutine. The conditional Call and Return instructions also can test condition flags.

(v) Machine Control Operations : These instructions control machine functions such as Halt, Interrupt, or do nothing. The microprocessor operations related to data manipulation can be summarized in four functions:

- 1. copying data

- 2. performing arithmetic operations

- 3. performing logical operations

- 4. testing for a given condition and alerting the program sequence

Some important aspects of the instruction set are noted below:

1. In data transfer, the contents of the source are not destroyed; only the contents of the destination are changed. The data copy instructions do not affect the flags.

2. Arithmetic and Logical operations are performed with the contents of the accumulator, and the results are stored in the accumulator (with some expectations). The flags are affected according to the results.

3. Any register including the memory can be used for increment and decrement.

4. A program sequence can be changed either conditionally or by testing for a given data condition.

#### **2.7. Instruction Format**

An instruction is a command to the microprocessor to perform a given task on a specified data. Each instruction has two parts: one is task to be performed, called the operation code (opcode), and the second is the data to be operated on, called the operand. The operand (or data) can be specified in various ways. It may include 8-bit (or 16-bit ) data, an internal register, a memory location, or 8-bit (or 16-bit) address. In some instructions, the operand is implicit.

### Instruction word size

The 8085 instruction set is classified into the following three groups according to word size:

- (i). One-word or 1-byte instructions

- (ii). Two-word or 2-byte instructions

- (iii). Three-word or 3-byte instructions

In the 8085, "byte" and "word" are synonymous because it is an 8-bit microprocessor. However, instructions are commonly referred to in terms of bytes rather than words.

(i) **One-Byte Instructions:** A 1-byte instruction includes the opcode and operand in the same byte. Operand(s) are internal register and are coded into the instruction.

#### For example:

| Task                                                                    | Opcode | Operand | <b>Binary Code</b> | Hex Code |

|-------------------------------------------------------------------------|--------|---------|--------------------|----------|

| Copy the contents of<br>the accumulator in<br>the register C.           | MOV    | С, А    | 0100 1111          | 4FH      |

| Add the contents of<br>register B to the contents<br>of the accumulator | ADD    | В       | 1000 0000          | 80H      |

| Invert (compliment) each bit in the accumulator.                        | CMA    |         | 0010 1111          | 2FH      |

These instructions are 1-byte instructions performing three different tasks. In the first instruction, both operand registers are specified. In the second instruction, the operand B is specified and the accumulator is assumed. Similarly, in the third instruction, the accumulator is assumed to be the implicit operand. These instructions are stored in 8-bit binary format in memory; each requires one memory location.

(ii) **Two-Byte Instructions:** In a two-byte instruction, the first byte specifies the operation code and the second byte specifies the operand. Source operand is a data byte immediately following the opcode.

#### For example:

| Task                                       | Opcode | Operand | <b>Binary Code</b> | Hex Code           |

|--------------------------------------------|--------|---------|--------------------|--------------------|

| Load an 8-bit data byte in the accumulator | MVI    | A, Data | 0011 1110          | 3E (First byte)    |

|                                            |        |         | Data               | Data (Second Byte) |

Assume that the data byte is 32H. The assembly language instruction is written as

| Mnemonics  | Hex code |

|------------|----------|

| MVI A, 32H | 3E, 32H  |

(iii) Three-Byte Instructions : In a three-byte instruction, the first byte specifies the opcode, and the following two bytes specify the 16-bit address. Note that the second byte is the low-order address and the third byte is the high-order address. opcode + data byte + data byte

#### For example:

| Task                                                             | Opcode | Operand | Hex Code                                            |

|------------------------------------------------------------------|--------|---------|-----------------------------------------------------|

| Transfer the program<br>sequence to the memory<br>location 2085H | JMP    | 2085H   | C3- First byte<br>85- Second Byte<br>20- Third Byte |

This instruction would require three memory locations to store in memory. Three byte instructions - opcode + data byte + data byte

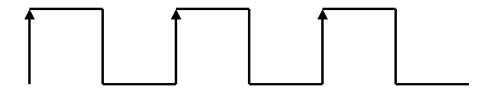

#### 2.8. Clock cycle

The speed of a computer processor, or CPU, is determined by the clock cycle (Fig.2.1), which is the amount of time between two pulses of an oscillator. Generally speaking, the higher number of pulses per second, the faster the computer processor will be able to process information. The clock speed is measured in Hz, typically either megahertz (MHz) or gigahertz (GHz). For example, a 4GHz processor performs 4,000,000,000 clock cycles per second.

Computer processors can execute one or more instructions per clock cycle, depending on the type of processor. Early computer processors and slower processors can only execute one instruction per clock cycle, but faster, more advanced processors can execute multiple instructions per clock cycle, processing data more efficiently.

Fig.2.1.: Clock Signal

#### 2.9. Machine cycle:

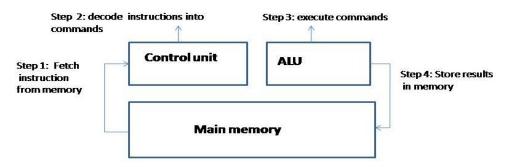

The steps performed by the computer processor for each machine language instruction received. The machine cycle is a 4 process cycle that includes reading and interpreting the machine language, executing the code and then storing that code.

#### Four steps of Machine cycle:

- 1. Fetch Retrieve an instruction from the memory.

- 2. Decode Tranlate the retrieved instruction into a series of computer commands.

- 3. Execute Execute the computer commands.

- 4. Store Save and write the results back in memory.

#### **Machine** Cycle

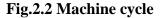

Each machine cycle is composed of many clock cycle. Since, the data and instructions, both are stored in the memory, the  $\mu$ P performs fetch operation to read the instruction or data and then execute the instruction. The  $\mu$ P in doing so may take several cycles to perform fetch and execute operation. The 3-status signals : IO / M, S1, and S0 are generated at the beginning of each machine cycle. The unique combination of these 3-status signals identify read or write operation and remain valid for the duration of the cycle. Table-2.1 shows details of the unique combination of these status signals to identify different machine cycles.

|                                                                       | Status |                |                | Controls |    |      |  |

|-----------------------------------------------------------------------|--------|----------------|----------------|----------|----|------|--|

| Machine cycle                                                         | IO/M   | S <sub>1</sub> | S <sub>0</sub> | RD       | WR | INTA |  |

| Opcode Fetch (OF)                                                     | 0      | 1              | 1              | 0        | 1  | 1    |  |

| Memory Read                                                           | 0      | 1              | 0              | 0        | 1  | 1    |  |

| Memory Write                                                          | 0      | 0              | 1              | 1        | 0  | 1    |  |

| I/O Read (I/OR)                                                       | 1      | 1              | 0              | 0        | 1  | 1    |  |

| I/O Write (I/OW)                                                      | 1      | 0              | 1              | 1        | 0  | 1    |  |

| Acknowledge of INTR (INTA)                                            | 1      | 1              | 1              | 1        | 1  | 0    |  |

| BUS Idle (BI) : DAD                                                   | 0      | 1              | 0              | 1        | 1  | 1    |  |

| ACK of RST, TRAP                                                      | 1      | 1              | 1              | 1        | 1  | 1    |  |

| HALT                                                                  | Z      | 0              | 0              | Z        | Z  | 1    |  |

| HOLD                                                                  | Ζ      | X              | Х              | Ζ        | Z  | 1    |  |

| $X \Rightarrow$ Unspecified, and $Z \Rightarrow$ High impedance state |        |                |                |          |    |      |  |

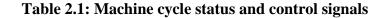

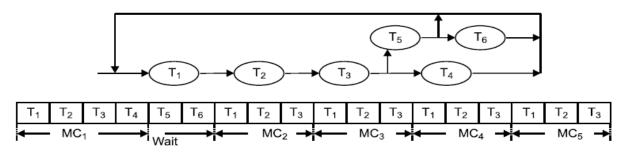

Thus, time taken by any  $\mu$ P to execute one instruction is calculated in terms of the clock period. The execution of instruction always requires read and writes operations to transfer data to or from the  $\mu$ P and memory or I/O devices. Each read/ write operation constitutes one machine cycle (MC1) as indicated in Fig. 2.3. Each machine cycle consists of many clock periods/ cycles, called T-states. Each and every operation inside the microprocessor is under the control of the clock cycle. The clock signal determines the time taken by the microprocessor to execute any instruction. The clock cycle shown in Fig. 2.3 has two edges (leading and trailing or lagging). State is defined as the time interval between 2-trailing or leading edges of the clock. Machine cycle is the time required to transfer data to or from memory or I/O devices.

Fig.2.3 Machine cycles showing clock periods

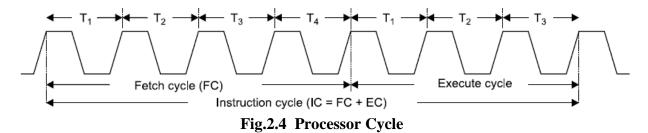

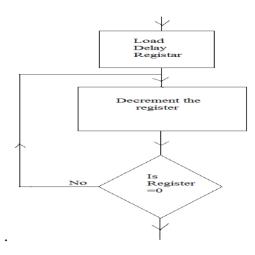

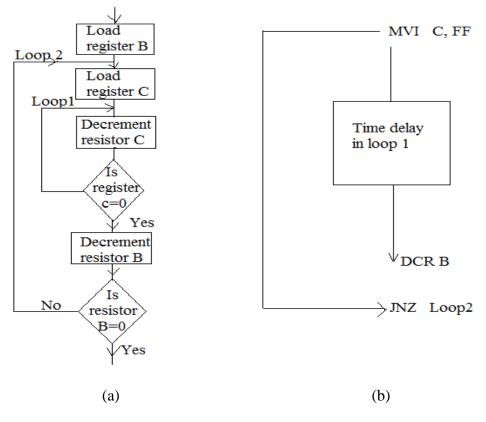

#### 2.10. Processor cycle - Instruction cycle

The function of the microprocessor is divided into fetch and execute cycle of any instruction of a program. The program is nothing but number of instructions stored in the memory in sequence. In the normal process of operation, the microprocessor fetches (receives or reads) and executes one instruction at a time in the sequence until it executes the halt (HLT) instruction. Thus, an instruction cycle is defined as the time required to fetch and execute an instruction. For executing any program, basically 2-steps are followed sequentially with the help of clocks

- 1. Fetch, and

- 2. Execute.

The time taken by the  $\mu$ P in performing the fetch and execute operations are called *fetch and execute cycle*. Thus, sum of the fetch and execute cycle is called the *instruction cycle* as indicated in Fig. 2.4.

Instruction Cycle (IC) = Fetch cycle (FC) + Execute Cycle (EC)

*Instruction Fetch* (*FC*)  $\Rightarrow$  An instruction of 1 or 2 or 3-bytes is extracted from the memory locations during the fetch and stored in the  $\mu$ P's instruction register.

Instruction Execute (EC)  $\Rightarrow$  The instruction is decoded and translated into specific activities during the execution phase. Thus, in an instruction cycle, instruction fetch, and instruction execute cycles are related as depicted in Fig. 2.4. Every instruction cycle consists of 1, 2, 3, 4 or 5-machine cycles as indicated in Fig. 2.5. One machine cycle is required each time the  $\mu$ P access memory or I/O port. The fetch cycle, in general could be 4 to 6-states whereas the execute cycle could of 3 to 6-states. The 1st machine cycle of any instruction is always the fetch cycle that provides identification of the instruction to be executed.

The fetch portion of an instruction cycle requires one machine cycle for each byte of instruction to be fetched. Since instruction is of 1 to 3 bytes long, the instruction fetch is one to 3-machine cycles in duration. The 1st machine cycle in an instruction cycle is always an opcode fetch. The 8-bits obtained during an opcode fetch are always interpreted as the Opcode of an instruction. The machine cycle including wait states is shown in Fig. 2.5

#### Fig.2.5 Machine cycles including wait states

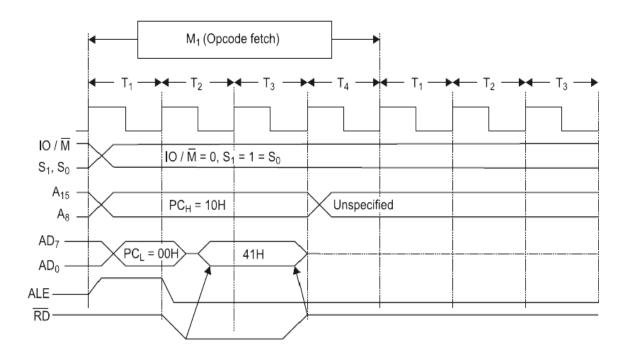

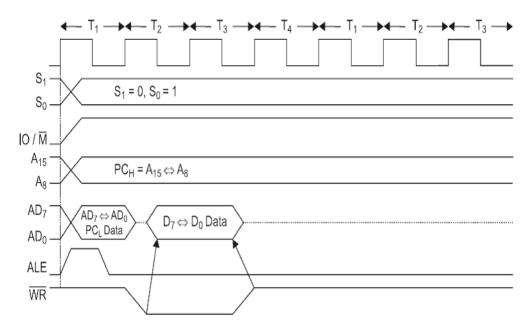

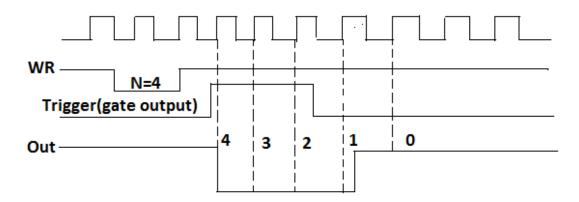

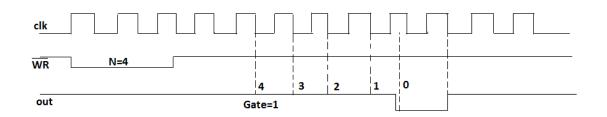

#### 2.11. Timing diagram of Opcode fetch

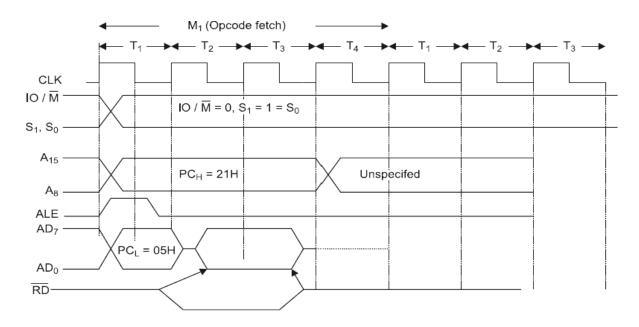

The process of opcode fetch operation requires minimum 4-clock cycles T1, T2, T3, and T4 and is the 1st machine cycle (M1) of every instruction.

#### Example

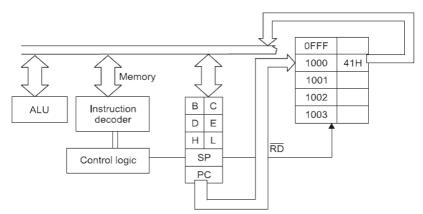

Fetch a byte 41H stored at memory location 2105H. For fetching a byte, the microprocessor must find out the memory location where it is stored. Then provide condition (control) for data flow from memory to the microprocessor. The process of data flow and timing diagram of fetch operation are shown in Figs. 2.6 (a), (b), and (c). The  $\mu$ P fetches opcode of the instruction from the memory as per the sequence below

- A low IO / M means microprocessor wants to communicate with memory.

- The  $\mu$ P sends a high on status signal S1 and S0 indicating fetch operation.

- The  $\mu$ P sends 16-bit address. AD bus has address in 1st clock of the 1st machine cycle,T1.

- AD7 to AD0 address is latched in the external latch when ALE = 1.

- AD bus now can carry data.

- In T2, the RD control signal becomes low to enable the memory for read operation.

- The memory places opcode on the AD bus

- The data is placed in the data register (DR) and then it is transferred to IR.

Fig. 2.6(a) Opcode Fetch

- During T3 the RD signal becomes high and memory is disabled.

- During  $T_4$  the opcode is sent for decoding and decoded in T4.

- The execution is also completed in T4 if the instruction is single byte.

- More machine cycles are essential for 2- or 3-byte instructions. The 1st machine cycle M1 is meant for fetching the opcode. The machine cycles M2 and M3 are required either to read/ write data or address from the memory or I/O devices.

### Example

Opcode fetch MOV B,C.

**T1**: The 1st clock of 1st machine cycle (M1) makes ALE high indicating address latch enabled which loads low-order address 00H on AD7 $\Leftrightarrow$ AD0 and high-order address 0H simultaneously on A15 $\Leftrightarrow$ A8. The address 00H is latched in T1.

**T2**: During T2clock, the microprocessor issues RD control signal to enable the memory and memory places 41H from 1000H location on the data bus. Fig. 2.6(b) Data flow from memory to microprocessor

Fig.2.6(b) Data flow from memory to microprocessor

**T3**: During T3, the 41H is placed in the instruction register and RD = 1 (high) disables signal. It means the memory is disabled in T3 clock cycle. The opcode cycle is completed by end of T3 clock cycle.

**T4**: The opcode is decoded in T4 clock and the action as per 41H is taken accordingly. In otherword, the content of C-register is copied in B-register. Execution time for opcode 41H is

Clock frequency of 8085 = 3.125 MHz Time (T) for one clock = 1/3.125 MHz = 325.5 ns = 0.32 µS

Execution time for opcode fetch =  $4T = 4*0.32 \ \mu S = 1.28 \ \mu S$

Fig.2.6 (c) Opcode fetch (MOV B,C)

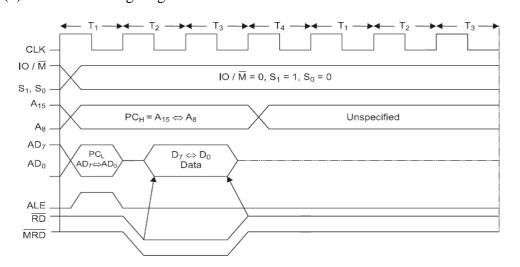

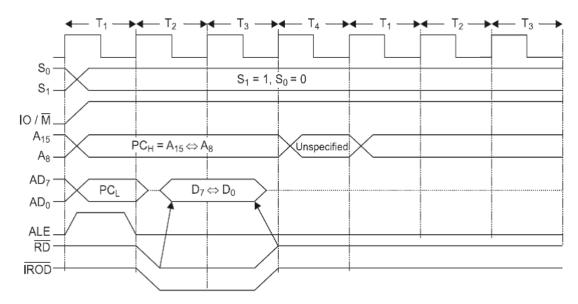

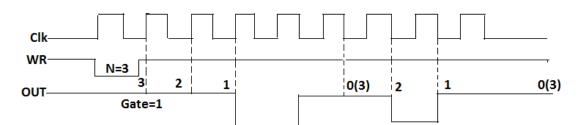

#### 2.12. Read Cycle

The high order address (A15  $\Leftrightarrow$ A8) and low order address (AD7 $\Leftrightarrow$ AD0) are asserted on 1st low going transition of the clock pulse. The timing diagram for IO/ M read are shown in Fig. 2.7 (a) and (b). The A15  $\Leftrightarrow$  A8 remains valid in T1, T2, and T3 i.e. duration of the bus cycle, but AD 7  $\Leftrightarrow$  AD0 remains valid only in T1. Since it has to remain valid for the whole bus cycle, it must be saved for its use in the T2 and T3. Fig. 2.7 (a) Memory read timing diagram ALE is asserted at the beginning of T1 of each bus cycle and is negated towards the end of T1. ALE is active during T1 only and is used as the clock pulse to latch the address (AD7 $\Leftrightarrow$ AD0) during T1. The RD is asserted near the beginning of T2. It ends at the end of T3. As soon as the RD becomes active, it forces the memory or I/O port to assert data. RD becomes inactive towards the end of T3, causing the port or memory to terminate the data. Fig. 2.7(b) I/O Read timing diagram

Fig.2.7(a) Memory read timing diagram

Fig. 2.7 (b) I/O Read Timing diagram

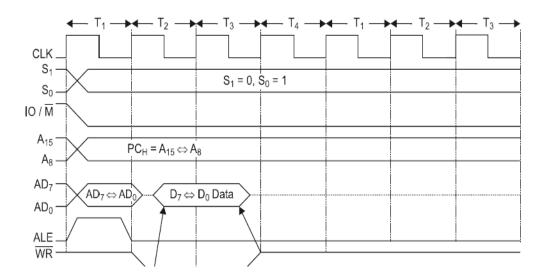

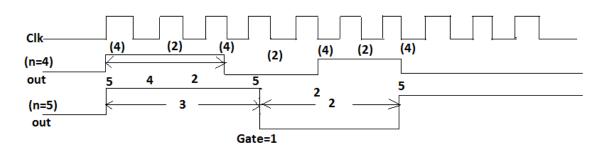

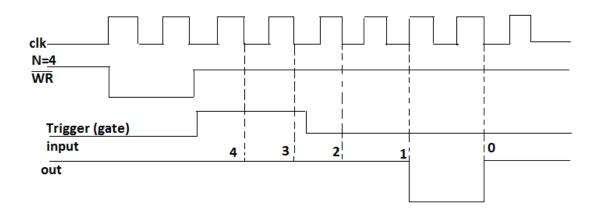

#### 2.13. Write Cycle

Immediately after the termination of the low order address, at the beginning of the T2, data is asserted on the address/data bus by the processor. WR control is activated near the start of T2 and becomes inactive at the end of T3. The processor maintains valid data until after WR is terminated. This ensures that the memory or port has valid data while WR is active. It is clear from Figs. 2.8 (a) and (b) that for READ bus cycle, the data appears on the bus as a result of activating RD and for the WR bus cycle, the time the valid data is on the bus overlaps the time that the WR is active. Fig. 2.8 (a) Memory write timing diagram. Fig. 2.8(b) I/O write timing diagram

Fig.2.8(a) Memory write timing diagram

Fig.2.8 (b) I/O write timing diagram

# 2.14 Programming the 8085A:

A Program is a set of instructions arranged in a sequence to do a specific task.

**Programming:** It is the process of writing the set of instructions.

**Assembly Language Programme:** The program with alphanumeric characters or mnemonic is known as assembly language program

Mnemonics: The program makes use of symbolic opcodes known as mnemonics.

An assembly language program (ALP) has the following fields:

Label

opcode

operand

comments

The ALP instruction format is shown below

| Label | opcode | operand | comments                             |

|-------|--------|---------|--------------------------------------|